# OPERATIONS MANUAL SAT-DX

# WinSystems - "The Embedded Systems Authority"

# **REVISION HISTORY**

# P/N 403-248-000

| ECO Number | Date Code | Rev Level |

|------------|-----------|-----------|

| ORIGINATED | 961017    | D         |

| 97-37      | 970602    | D1        |

| 97-106     | 971110    | D2        |

| 97-107     | 971110    | D3        |

| 97-113     | 971117    | E         |

| 98-16      | 980217    | E1        |

| 98-31      | 981006    | G         |

| 99-31      | 990721    | Н         |

| 99-84      | 001001    | I         |

| 01-23      | 010425    | I1        |

# TABLE OF CONTENTS

| Section<br>Number | Paragraph<br>Title            | Page<br>Number |  |  |

|-------------------|-------------------------------|----------------|--|--|

| 1                 | General Information           |                |  |  |

| 1 1               | Factorias                     | 1 1            |  |  |

| 1.1<br>1.2        | Features General Description  | 1-1<br>1-1     |  |  |

|                   | General Description           |                |  |  |

| 1.3               | Specifications                | 1-2            |  |  |

| 2                 | SAT-DX Technical Reference    |                |  |  |

| 2.1               | Introduction                  | 2-1            |  |  |

| 2.2               | Processor Selection           | 2-1            |  |  |

| 2.3               | ALI 1487/1489 Chipset         | 2-2            |  |  |

| 2.4               | Processor Speed Selection     | 2-2            |  |  |

| 2.5               | Memory Installation/Selection | 2-3            |  |  |

| 2.6               | Real Time Clock/Calendar      | 2-4            |  |  |

| 2.7               | Keyboard Interface            | 2-5            |  |  |

| 2.8               | Serial Interface              | 2-5            |  |  |

| 2.9               | Parallel Printer Interface    | 2-10           |  |  |

| 2.10              | Speaker/Sound Interface       | 2-11           |  |  |

| 2.11              | PC/104 Bus Interface          | 2-11           |  |  |

| 2.12              | Floppy Disk Interface         | 2-12           |  |  |

| 2.13              | IDE Hard Disk Interface       | 2-12           |  |  |

| 2.14              | Watchdog Timer Configuration  | 2-13           |  |  |

| 2.15              | Battery Select Control        | 2-14           |  |  |

| 2.16              | Power/Reset Connections       | 2-14           |  |  |

| 2.17              | Interrupt Routing             | 2-15           |  |  |

| 2.18              | Silicon Disk Configuration    | 2-16           |  |  |

| 2.19              | Parallel I/O                  | 2-18           |  |  |

| 2.20              | I/O Connector                 | 2-19           |  |  |

| 2.21              | Jumper/Connector Summary      | 2-20           |  |  |

| 3                 | Award BIOS Configuration      |                |  |  |

| 3.1               | General Information           | 3-1            |  |  |

| 3.2               | Entering Setup                | 3-1            |  |  |

| 3.3               | Setup Main Menu               | 3-1            |  |  |

| 3.4               | Standard CMOS Setup           | 3-2            |  |  |

| 3.5               | BIOS Features Setup           | 3-6            |  |  |

| 3.6               | Chipset Features Setup        | 3-9            |  |  |

| 3.7               | Load BIOS Defaults            | 3-13           |  |  |

| 3.8               | Load Setup Defaults           | 3-13           |  |  |

| 3.9               | Password Setting              | 3-13           |  |  |

| 3.10              | IDE HDD Auto Detection        | 3-13           |  |  |

| 3.11              | Save & Exit Setup             | 3-13           |  |  |

| 3.12              | Exit without Saving 3-13      |                |  |  |

# WinSystems - "The Embedded Systems Authority"

| 4          | SAT-DX Silicon Disk Reference |     |

|------------|-------------------------------|-----|

| 4.1        | Introduction                  | 4-1 |

| 4.2        | ROMDISK usage                 | 4-1 |

| 4.3        | Bootable RAMDISK usage        | 4-4 |

| 4.4        | Non-Bootable RAMDISK usage    | 4-5 |

| 4.5        | Non-Bootable FLASHDISK usage  | 4-7 |

| 4.6        | DiskOnChip usage              | 4-7 |

| APPENDIX A | Port I/O Map                  |     |

| APPENDIX B | Interrupt Map                 |     |

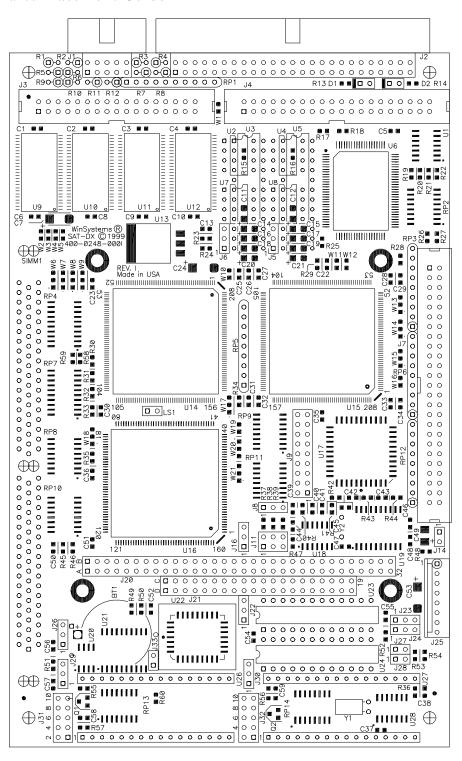

| APPENDIX C | SAT-DX Parts Placement Guide  |     |

| APPENDIX D | SAT-DX Parts List             |     |

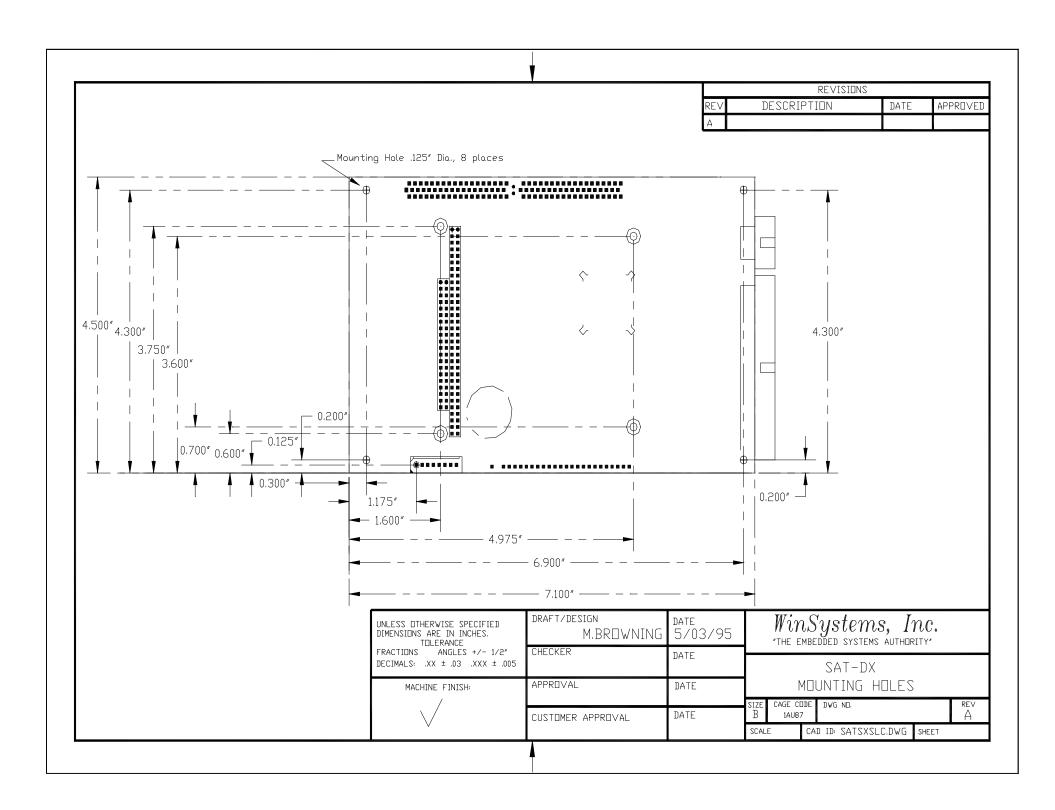

| APPENDIX E | SAT-DX Mechanical Drawing     |     |

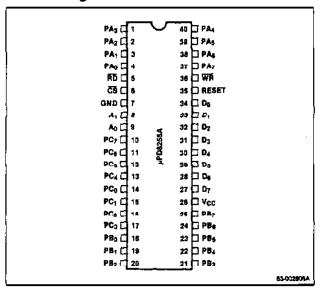

| APPENDIX F | 8255 Datasheet Reprint        |     |

# 1 GENERAL INFORMATION

### 1.1 FEATURES

- 80486DX4-100 Processor Selection

- 100% PC/AT Hardware/Software Compatibility

- Up to 64 MBytes of DRAM supported

- User installable SIMM DRAM modules or factory installed ruggedized DRAM

- Onboard Solid State Disk for EPROM, PEROM, SRAM or FLASH

- Industry Standard Award BIOS with POST

- Two 16550 Compatible UARTS with RS-232 and optional RS-422/RS-485 Support

- Bi-directional LPT port supports EPP and ECP modes

- 24 Multipurpose Digital I/O Lines

- Onboard Local Bus IDE interface

- Onboard Floppy Disk Controller

- 16-Bit PC/104 Bus Expansion

- Watchdog Timer with Powerfail/Brownout Monitoring

- Status and Hard Disk Activity LEDs

- 5 Volt Only Operation

# 1.2 GENERAL DESCRIPTION

The SAT-DX is a small, high-performance embeddable computer system on a single board. Its full PC/AT hardware complement and industry standard AWARD BIOS assures full hardware and software compatibility with PC software and operating systems. The SAT-DX includes onboard interfaces for floppy disks, IDE fixed disks, Parallel printer, and two serial channels with RS-232, RS-422, or RS-485 capability on either or both channels. A full 16-bit PC/104 expansion bus is provided for further expansion to an entire industry of add-on peripherals including high-speed VGA controllers, sound and speech modules, SCSI controllers, Analog I/O modules, and literally hundreds of other options available from WinSystems and a variety of vendors supporting the PC/104 standard. User installable/upgradeable 72-pin SIMM DRAM modules are supported up to a maximum of 64 Megabytes. Optional factory installed DRAM is also available for applications that may be intolerant to the limitations of the SIMM modules lack of ruggedness. An onboard Silicon Disk array supports disks of up to 2 Megabytes in size and can utilize SRAM, PEROM or EPROM as the disk media. Boot capability is provided onboard and a set of utilities and drivers are provided to make the silicon disk based system very user friendly. Alternately, the M-Systems' DiskOnChip FLASH modules may be populated, supporting disk sizes ranging from 2 Megabytes to 72 Megabytes.

# 1.3 Specifications

#### **1.3.1** Electrical

Bus Interface: PC/104 8-Bit and 16-Bit expansion bus

System Clock: Jumper programmable from 4MHz to 50MHz

Interrupts: TTL Level input

VCC: +5V +/-5% at 1000mA typical with 486DX4-100 and 8MB DRAM

VCC1: +12V +/-5% (Not required. PC/104 Expansion Only)

VCC2: -12V +/-5% (Not Required. PC/104 Expansion Only)

#### **1.3.2** Memory :

Addressing: 64 Megabyte addressing

BIOS ROM: 128K OTPROM

Memory SIMM Socket: 72-Pin Standard or EDO DRAM in sizes from 1M to 32M

SSD Memory: Two 32-pin JEDEC standard sockets support 4-MBit SRAM, 4-MBit PEROM,

4-MBit EPROM, 8-MBit EPROM or one M-Systems 32-pin DOC

(DiskOnChip) Module.

#### **1.3.3** Mechanical

Dimensions: 4.5 X 7.1 X .60 inches (without PC/104 modules or cables)

PC-Board: FR4 Epoxy Glass with 6 signal layers and 2 power planes with screened

component legend, and plated through holes.

Jumpers: 0.025" square posts on 0.10" centers

Connectors: Multi I/O: 50 pin RN type IDH-50-LP

RS-422/RS-485: 10 Pin RN type IDH-10-LP

Floppy Disk: 34 Pin RN type IDH-34-LP

Fixed Disk: 40 pin RN type IDH-40-LP

PC/104 BUS: 64 pin SAMTECH type ESQ-132-12-G-D

40 pin SAMTECH type ESQ-120-12-G-D

Power/Reset Connector: 8 Pin Molex

#### WinSystems - "The Embedded Systems Authority"

#### **1.3.4** Environmental

Operating Temperature : 0° to +60°C

**NOTE**: The operating temperature specification is highly dependent upon the type and speed of the CPU installed and any heat- sinking or cooling air flow supplied. The CPU case and junction temperature, as specified by the manufacturer, will be the limiting factors on this product.

Non-Condensing Humidity: 5 to 95%

WinSystems - "The Embedded Systems Authority"

THIS PAGE INTENTIONALLY LEFT BLANK

# 2 SAT-DX Technical Reference

# 2.1 Introduction

This section of the manual is intended to provide sufficient information regarding the configuration and usage of the SAT-DX board. Win Systems maintains a Technical Support group to help answer questions regarding configuration, usage, or programming of the board. For answers to questions not adequately addressed in this manual contact Technical Support at (817) 274-7553 between 8AM and 5PM Central Time.

# 2.2 Processor Selection

The SAT may be populated with any of a variety of 486 compatible processors from CY-RIX, AMD, or INTEL. The CPUs are surface mount devices and are factory installed. There are no user configuration jumpers for CPU type. The following configuration table is provided for reference purposes.

| Jumpering | S486DX2-66 | S486DX4-100 | AMD-X5-133S | AM486DE2-66 | INTEL DX2-50 |

|-----------|------------|-------------|-------------|-------------|--------------|

| W15, 1-2  | INSTALLED  | OPEN        | INSTALLED   | INSTALLED   | OPEN         |

| W15, 2-3  | OPEN       | INSTALLED   | OPEN        | OPEN        | OPEN         |

| W11       | INSTALLED  | INSTALLED   | INSTALLED   | OPEN        | OPEN         |

| W12       | INSTALLED  | INSTALLED   | INSTALLED   | INSTALLED   | OPEN         |

| W21, 1-2  | OPEN       | OPEN        | OPEN        | OPEN        | OPEN         |

| W21, 2-3  | INSTALLED  | INSTALLED   | INSTALLED   | INSTALLED   | INSTALLED    |

| W19       | INSTALLED  | INSTALLED   | INSTALLED   | INSTALLED   | INSTALLED    |

| W14, 1-2  | OPEN       | OPEN        | OPEN        | INSTALLED   | INSTALLED    |

| W14, 2-3  | INSTALLED  | INSTALLED   | INSTALLED   | OPEN        | OPEN         |

| W10       | OPEN       | OPEN        | OPEN        | OPEN        | OPEN         |

| W20, 2-3  | OPEN       | OPEN        | OPEN        | OPEN        | OPEN         |

| W20, 1-2  | INSTALLED  | INSTALLED   | INSTALLED   | INSTALLED   | OPEN         |

| W13, 1-2  | OPEN       | OPEN        | OPEN        | OPEN        | OPEN         |

| W13, 2-3  | INSTALLED  | INSTALLED   | INSTALLED   | INSTALLED   | OPEN         |

# 2.3 ALI 1487/1489 Chipset

The SAT-DX utilizes the ALI FINALI-486 Chipset which provides a highly integrated high-performance backbone for full PC/AT compatibility. The chipset contains the logic for DRAM and bus state control as well as the standard complement of 'AT' class peripherals internally, including:

8 DMA Channels compatible with PC-AT 8237A DMA Controllers

15 Interrupt inputs compatible with master/slaved 8259 interrupt controllers

Three 8254 compatible timer/counter channels

A PC-AT compatible real time clock/calendar with CMOS RAM

A Local BUS IDE interface

A PC-AT compatible Keyboard interface

The functional units are 100% PC-AT compatible and are supported by the AWARD BIOS and Setup. Users desiring to access these internal peripherals directly should refer to any manufacturer's generic literature on the equivalent discrete component.

There are a number of internal registers within the Finali-486 Chipset that are used by the BIOS for control and configuration. Refer to the I/O Map in Appendix A for port usage to avoid conflicts when adding external I/O devices.

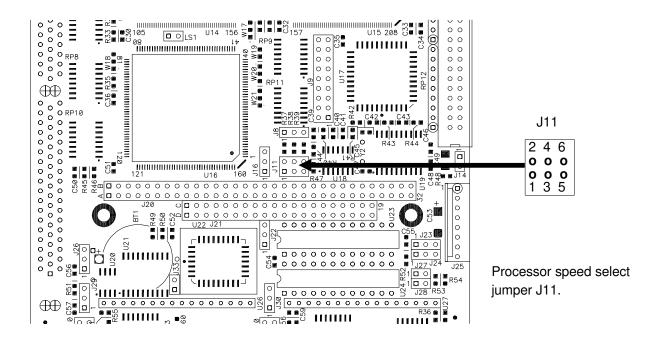

# 2.4 Processor Speed Selection

The SAT-DX uses a crystal controlled frequency synthesizer to control the CPU clock rate. The jumper block at J11 allows for the selection of any of 8 CPU clock frequencies ranging from 4Mhz to 50Mhz. The table below gives all of the possible CPU clock speeds available.

| Speed Select Jumper J11 |          |          |          |

|-------------------------|----------|----------|----------|

| CPU Speed               | Pins 1-2 | Pins 3-4 | Pins 5-6 |

| 4MHz                    | ON       | ON       | ON       |

| 8MHz                    | OFF      | ON       | ON       |

| 16MHz                   | ON       | OFF      | ON       |

| 20MHz                   | OFF      | OFF      | ON       |

| 25MHz                   | ON       | ON       | OFF      |

| 33MHz                   | OFF      | ON       | OFF      |

| 40MHz                   | ON       | OFF      | OFF      |

| 50MHz                   | OFF      | OFF      | OFF      |

**NOTE:** The SAT-DX board will be jumpered at the factory for the rated speed of the installed processor. Jumpering J11 to any speed in excess of the rated speed may result in CPU overheating, misoperation, and possible destruction of the CPU. Failures of CPUs which have been exposed to frequencies above their rated speed or to temperatures above their rated value will not be covered under the WinSystems standard product warranty.

# 2.5 Memory Installation Selection

The SAT-DX utilizes DRAM memory in one of two forms, either 72-pin standard SIMM modules in sizes of 1 Megabyte to 64 Megabytes are usable or factory installed SMT memory in sizes of 4, 8, 16, or 32 Megabytes.

When no factory DRAM is provided, the SAT-DX allows for user installation of standard 72-pin (32-bit wide) SIMM DRAM modules in 70nS or 60nS speeds. These are the standard SIMM modules used in most 32-bit 386 and 486 based desktop personal computers. These memory modules range in size from 1 Megabyte to 64 Megabytes in size.

### Go to <a href="http://www.winsystems.com/memory">http://www.winsystems.com/memory</a> for a list of qualified modules.

Installation is accomplished with power off by angling the SIMM module approximately 30 degrees from horizontal and inserting the fingers into the connector. The SIMM module is keyed slightly off-center and cannot be inserted backwards without extreme force. Once the fingers are in the socket the module is then rotated to the horizontal until the retaining clips snap into place. Removal is the reverse process. Pull the retaining clips outward and the SIMM module once released should rotate back to an appropriate removal angle.

SIMM modules should not be removed and reinserted any more often than necessary as the connectors were not designed for repeated use and intermittent operation may result because of insufficient contact or retaining force.

#### 2.6 Real Time Clock Calendar

The SAT-DX contains an onboard Clock/Calendar within the ALI 1487 chip. This clock is fully compatible with the MC146818A used in the original PC-AT computers. This clock has a number of features including periodic and alarm interrupt capabilities. In addition to the Time and Date keeping functions the system configuration is kept in CMOS RAM contained within the clock section. This RAM holds all of the setup information regarding hard and floppy disk types, video type, shadowing, wait states, etc. Refer to the section on the Award BIOS Setup for complete information on what is configured via the CMOS RAM.

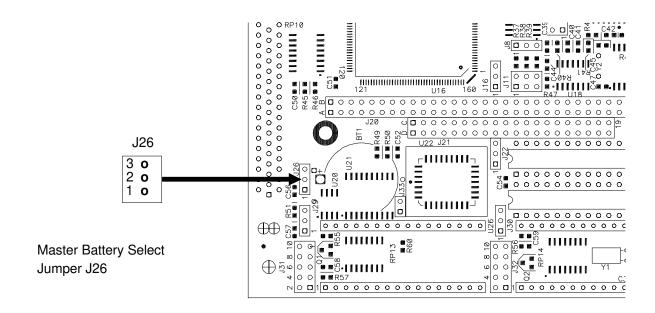

It may become necessary at some time to make the CMOS RAM forget its current configuration and to start fresh with factory defaults. This may be accomplished by removing power and the board from the system. Then remove the jumper from J26 pins 1-2 and place it on J26 pins 2-3 for approximately 10 seconds. Replace the jumper to its original position on pins 1-2, reinstall the board, power up, and reconfigure the CMOS setup as desired.

# 2.7 Keyboard Interface

The SAT-DX contains an onboard PC-AT style keyboard controller. Connection is made through the multi-I/O connector at J2. An adapter cable P/N CBL-162-1 is available from WinSystems to make ready access to all of the devices terminated at the multi-I/O connector. Users desiring custom connections should refer to the multi-I/O connector pin definitions given later in this manual.

### 2.8 Serial Interface

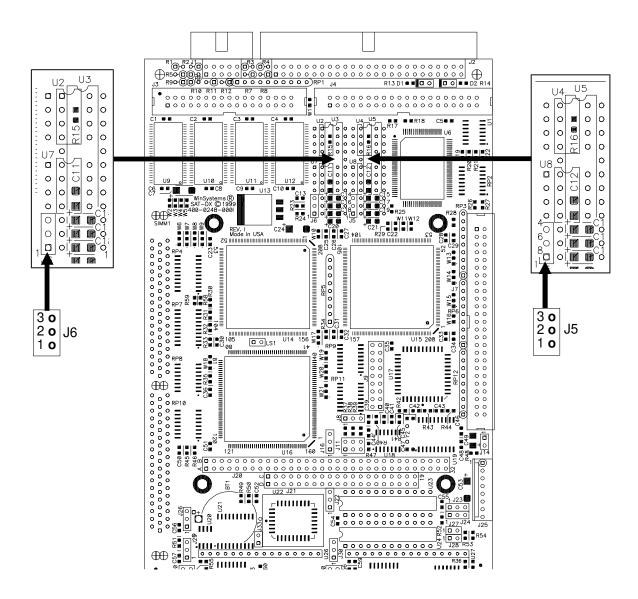

The SAT-DX provides two RS-232 serial channels onboard, configurable as RS-422 or RS-485 with the addition of optional driver ICs. The configuration options for each of the supported modes are shown on the following pages.

### **2.8.1** COM 1 - RS-232

| Jumper Position   | <b>Driver IC Status</b>                                    | I/O Connector Pin                                                             |

|-------------------|------------------------------------------------------------|-------------------------------------------------------------------------------|

| J6                |                                                            | COM1 DB9                                                                      |

| 3 o<br>2 o<br>1 o | U2 - Not Installed<br>U3 - Installed<br>U7 - Not Installed | CD 1 0 0 6 DSR RX Data 2 0 0 7 RTS TX Data 3 0 0 8 CTS DTR 4 0 0 9 RI GND 5 0 |

#### **2.8.2** COM 2 - RS-232

| <b>Jumper Position</b> | <b>Driver IC Status</b>                                    | I/O Connector Pin                                                             |

|------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------|

| J5                     |                                                            | COM2 DB9                                                                      |

| 3 o<br>2 o<br>1 o      | U4 - Not Installed<br>U5 - Installed<br>U8 - Not Installed | CD 1 0 0 6 DSR RX Data 2 0 0 7 RTS TX Data 3 0 0 8 CTS DTR 4 0 0 9 RI GND 5 0 |

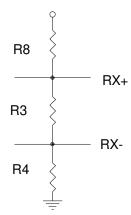

### **2.8.3** RS-422 Mode Configuration

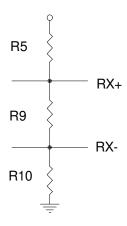

RS-422 Signal levels are supported on either or both serial channels with the installation of the optional "Chip Kit" WinSystems' part number CK-75176-2. This kit provides the driver ICs necessary for a single channel of RS-422. If two channels of RS- 422 are required then two kits will be needed. RS-422 is a 4-wire point to point full-duplex interface allowing much longer cable runs than are possible than with RS-232. The differential transmitter and receiver twisted-pairs offer a high degree of noise immunity. RS-422 usually requires that the lines be terminated at both ends. This termination can be accomplished either on the cable or by installing resistors on the board in locations reserved for them. The methodology for determining the correct resistor values is beyond the scope of this document but it is recommended the trial values of 100 ohms be used in all three locations at the receiver end. The following illustrations show the correct jumpering, driver IC installation, I/O connector pin definitions, and termination resistor locations for each of the channels when used in RS-422 mode.

### **2.8.4** COM 1 - RS-422

| Jumper Position         | Driver IC Status                                       | I/O Connector Pin                                                             |

|-------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------|

| J6<br>3 o<br>2 o<br>1 o | U2 - Installed<br>U3 - Not Installed<br>U7 - Installed | J1  TX+ 1 0 0 2  RX+ 3 0 0 4  RX- GND 5 0 0 6  N/A 7 0 0 8  N/A 9 0 0 10  N/A |

**RS-422 NOTE:** When used in RS-422 mode, the transmitter must be enabled by setting the RTS bit in the Modem Control Register (Bit 1).

#### **2.8.5** COM 2 - RS-422

| <b>Jumper Position</b>           | <b>Driver IC Status</b>                                | I/O Connector Pin                                                                   |

|----------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------|

| J5                               |                                                        | J1                                                                                  |

| 3 <b>o</b> 2 <b>o</b> 1 <b>o</b> | U4 - Installed<br>U5 - Not Installed<br>U8 - Installed | N/A 1 0 0 2<br>N/A 3 0 0 4<br>N/A<br>GND 5 0 0 6<br>TX+ 7 0 0 8<br>RX+ 9 0 0 10 RX- |

**RS4-22 NOTE:** When used in RS-422 mode, the transmitter must be enabled by setting the RTS bit in the Modem Control Register (Bit 1).

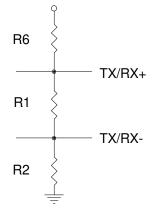

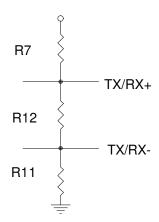

### **2.8.6** RS-485 Mode Configuration

The RS-485 multi-drop interface is supported on both serial channels with the installation of the optional "Chip Kit" WinSystems' part number CK-75176-2. A single kit is sufficient to configure both channels for RS-485. RS-485 is a 2-wire multi-drop interface where only one station at a time talks (transmits) while all others listen (receive). RS-485 usually requires the twisted line-pair be terminated at each end of the run. The required termination values are dependent upon a number of factors including: line impedance, line length, etc. A good trial value is 100 ohm resistors in all three locations. The following illustrations show the correct jumpering, driver IC installation, I/O connector pin-out, and termination resistor locations for each of the channels when used is RS-485 mode.

#### **2.8.7** COM 1 - RS-485

| Jumper Position  | <b>Driver IC Status</b>                                    | I/O Connector Pin<br>J1                                                                            |

|------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| J6<br>3 1<br>1 0 | U2 - Installed<br>U3 - Not Installed<br>U7 - Not Installed | TX/RX+ 1 0 0 2 TX/RX-<br>N/A 3 0 0 4 N/A<br>GND 5 0 0 6 +5V<br>N/A 7 0 0 8 N/A<br>N/A 9 0 0 10 N/A |

RS485 NOTE: Because RS-485 uses a single twisted-pair, all transmitters are connected in parallel. Only one station may transmit, or have its transmitter enabled at a time. The transmitter Enable/Disable is controlled by bit 1 in the Modem Control Register (RTS). When set, the transmitter is enabled, when cleared (the normal state) the transmitter is disabled and the receiver is enabled. Note that it is necessary to allow some minimal settling time after enabling the transmitter before transmitting the first character. Likewise, following a transmission, it is necessary to be sure that all characters have been completely shifted out of the UART (Check Bit 6 in the Line Status Register) before disabling the transmitter to avoid chopping off the last character.

### **2.8.8** COM 2 - RS-485

#### **Jumper Position Driver IC Status** I/O Connector Pin J1 J5 U4 - Installed N/A 3 2 N/A N/A 0 4 U5 - Not Installed 0 GND 5 0 0 6 +5V 1 **o** U8 - Not Installed TX/RX- $TX/RX+|7 \circ$ N/A N/A 9 **o** o 10

RS485 NOTE: Because RS-485 uses a single twisted-pair, all transmitters are connected in parallel. Only one station may transmit, or have its transmitter enabled at a time. The transmitter Enable/Disable is controlled by bit 1 in the Modem Control Register (RTS). When set, the transmitter is enabled, when cleared (the normal state) the transmitter is disabled and the receiver is enabled. Note that it is necessary to allow some minimal settling time after enabling the transmitter before transmitting the first character. Likewise, following a transmission, it is necessary to be sure that all characters have been completely shifted out of the UART (Check Bit 6 in the Line Status Register) before disabling the transmitter to avoid chopping off the last character.

#### 2.9 Parallel Printer Interface

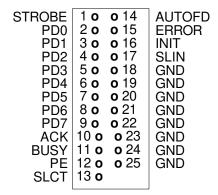

The SAT-DX supports a fully bi-directional parallel printer port capable of EPP and ECP operations. The parallel port is I/O mapped at 278H and is terminated at the multi-I/O connector J2. The pin definitions for the parallel port connector DB-25 when used with the CBL-162-1 cable is as shown below:

# **2.9.1** ECP DMA Configuration

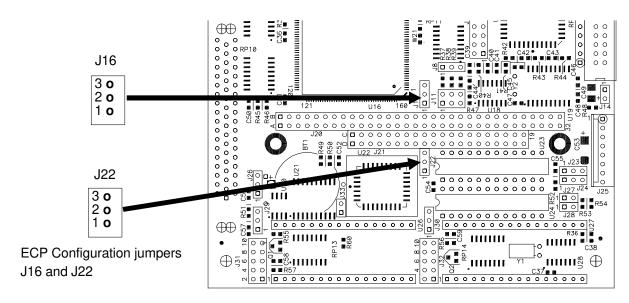

When the Parallel port is used in an ECP configuration, J 16 and J 22 are used to configure the DMA channel to be used for ECP transfers. DMA Channel 1 or Channel 3 is selectable as shown below:

# 2.10 Speaker/Sound Interface

The SAT-DX utilizes a high-impedance piezo type device for audio output. BIOS Beep codes, error signaling, or user defined tones can be presented via this device.

# 2.11 PC/104 Bus interface

The SAT-DX supports I/O expansion through the standard PC/104 connectors at J20 and J21. The SAT-DX supports both 8-bit and 16-bit PC/104 modules. The PC/104 connector pin definitions are provided here for reference purposes.

| J20                                                                                                                                                                                                                                              |    |                                                                                                                                                                                                                                                          |                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| GND<br>RESET<br>+5V<br>IRQ9<br>-5V<br>DRQ2<br>-12V<br>OWS<br>+12V<br>GND<br>MEMW<br>MEMR<br>IOW<br>IOR<br>DACK3<br>DACK1<br>DRQ1<br>REFRESH<br>SYSCLK<br>IRQ7<br>IRQ6<br>IRQ5<br>IRQ4<br>IRQ3<br>DACK2<br>TC<br>BALE<br>+5V<br>OSC<br>GND<br>GND | B1 | o A1<br>o A2<br>o A3<br>o A4<br>o A5<br>o A6<br>o A7<br>o A8<br>o A9<br>o A11<br>o A12<br>o A13<br>o A14<br>o A15<br>o A16<br>o A20<br>o A21<br>o A22<br>o A23<br>o A24<br>o A25<br>o A26<br>o A27<br>o A28<br>o A29<br>o A30<br>o A31<br>o A31<br>o A31 | IOCHK BD7 BD6 BD5 BD4 BD3 BD2 BD1 BD0 IOCHRDY AEN SA19 SA18 SA17 SA16 SA15 SA14 SA13 SA12 SA11 SA10 SA9 SA8 SA7 SA6 SA5 SA4 SA3 SA2 SA1 SA0 GND |

| GND<br>SBHE<br>LA23                                                                                                 | C0 o<br>C1 o<br>C2 o | o D0<br>o D1<br>o D2                                                                                         | GND<br>MEMCS16<br>IOCS16                                                                 |

|---------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| LA22<br>LA21<br>LA20<br>LA19<br>LA18<br>LA17<br>MEMR<br>MEMW<br>SD8<br>SD10<br>SD11<br>SD12<br>SD13<br>SD14<br>SD15 | C3                   | o D3<br>o D4<br>o D5<br>o D6<br>o D7<br>o D10<br>o D11<br>o D12<br>o D13<br>o D14<br>o D15<br>o D16<br>o D17 | IRQ10 IRQ11 IRQ12 IRQ15 IRQ14 DACK0 DRQ0 DACK5 DRQ5 DACK6 DRQ6 DACK7 DRQ7 VCC MASTER GND |

| KEY                                                                                                                 | C19 <b>o</b>         | <b>o</b> D19                                                                                                 | GND                                                                                      |

J21

# 2.12 Floppy Disk Interface

The SAT-DX supports up to 2 standard 3 1/2" or 5 1/4" PC compatible floppy disk drives. The drives are connected via the I/O connector at J3. Note that the interconnect cable to the drives is a standard floppy I/O cable used on desk-top PCs. The cable must have the twisted section prior to the drive A: position. The pin definitions for the J3 connector are shown here for reference.

|                                        | J                                                                          |                                                                                                          |                                                                                                                                            |

|----------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| GNDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD | 1 o 3 o 5 o 7 o 9 o 11 o 13 o 15 o 17 o 21 o 23 o 25 o 27 o 29 o 31 o 33 o | o 2<br>o 4<br>o 6<br>o 8<br>o 10<br>o 12<br>o 14<br>o 16<br>o 22<br>o 22<br>o 22<br>o 23<br>o 32<br>o 34 | RPM/LC<br>N/C<br>N/C<br>INDEX<br>MTR0<br>DRV1<br>DRV0<br>MTR1<br>DIR<br>STEP<br>WDATA<br>WGATE<br>TRK0<br>WPRT<br>RDATA<br>HDSEL<br>DSKCHG |

# 2.13 IDE Hard Disk Interface

The SAT-DX supports standard IDE fixed disks through the I/O connector at J4. A Red activity LED is present at D2. The pin definitions for the J4 connector are shown here:

# 2.14 Watchdog Timer Configuration

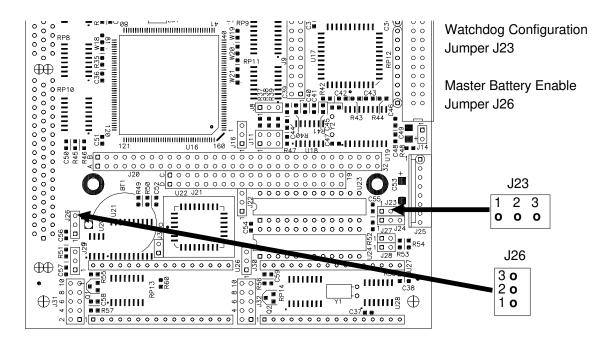

The SAT-DX board features a power-on voltage detect and a power-down/power brown-out reset circuit to protect memory and I/O from faulty CPU operation during periods of illegal voltage levels. This supervisory circuitry also features a watchdog timer which can be used to guard against software lockups. An internal self-timer with a period of 1.5 seconds will, when enabled, reset the CPU is the watchdog has not been serviced (petted) within the allotted time. There are three watchdog operational modes available on the SAT-DX. With no jumper installed on J23, the watchdog is totally disabled and can never reset the CPU. When J23 is jumpered pins 2-3, the watchdog circuit is permanently enabled and timing begins immediately with power-on. This mode is NOT compatible with the Award BIOS or with MS-DOS, but is available for directly embedded code that takes the place of the BIOS. The watchdog must be accessed at least every 1.5 seconds or a reset will occur. Petting in this mode is accomplished by writing to I/O port 1D0H with an alternating 1 and 0 value.

The alternate mode of operation is via software enable/disable control. This mode is set by jumpering J23, pins 1-2. In this mode the watchdog timer powers-up disabled and must be enabled in software before timing will begin. Enabling is accomplished by writing a 1 to I/O port 1D0H. Writing a 0 to I/O port 1D0H will disable the watchdog. After enabling the watchdog must be serviced at least every 1.5 seconds or a reset will occur. The petting is accomplished in either of 2 ways. The first method is to read port 1D8H and XOR the value read with 1 and rewrite the result to I/O port 1D8H. The second method is to do two consecutive writes to port 1D8H with a value of 0 followed by a value of 1. This mode of operation can be used with the BIOS and DOS provided that the watchdog is disabled before making any extensive BIOS or DOS calls, especially video or Disk I/O calls, which in some cases could exceed the 1.5 seconds allowed. The drawback to this mode is that a lockup dur-

ing the time the watchdog is disabled will not allow for auto-recovery but will require an external source for a reset.

# 2.15 Battery Select Control

The SAT-DX has an onboard lithium battery used to sustain the Clock/Calendar CMOS setup information, and Solid State Disk information when SRAMs are used. A master battery enable jumper is provided at J26. With J26 jumpered pins 2-3 the battery is totally disconnected and no battery voltage is supplied to any circuitry on the board. Individual sockets in the Solid State Disk array may be jumpered for battery backup when using SRAMs if desired. Refer to the Silicon Disk Configuration section of this manual for details. It may become necessary or desirable at some time to erase the CMOS setup information due to incorrect or undesirable settings which are causing an inability to execute the setup utility or improper operation. To reset the CMOS memory to factory defaults, move the jumper from J26 pins 1-2 and place the jumper on J26 pins 2-3 for at least 10 seconds and then restore the jumper to the normal position on pins 1-2. This should result in the BIOS restoring defaults and prompting for setup during the next boot. Refer to section 3: Award BIOS Configuration for setup options and details.

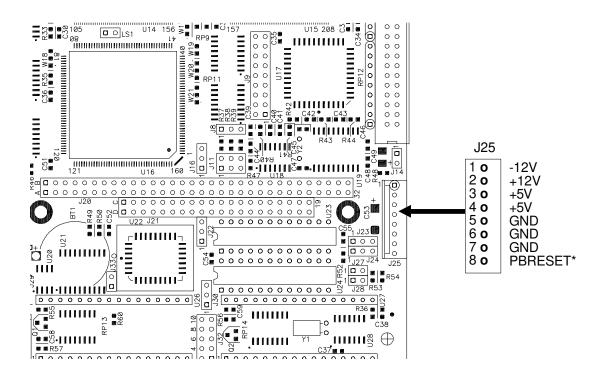

#### 2.16 Power/Reset Connections

Power is applied to the SAT-DX via the connector at J25. The pin definitions for J25 are given below. An optional push-button-reset may also be routed into J25 if desired.

# 2.17 Interrupt Routing

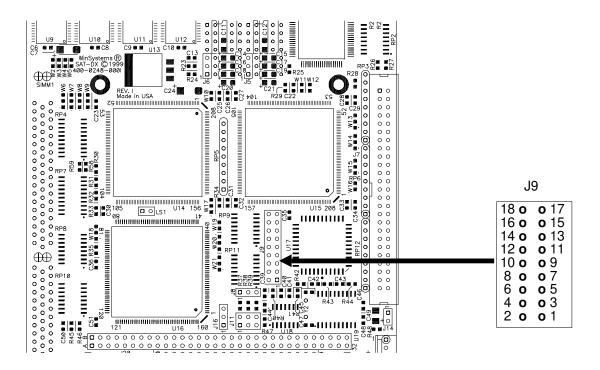

All interrupt inputs are routed to their respective PC/104 bus pins as shown earlier in the PC/104 bus interface section. Onboard peripherals, Serial, Parallel, and Disk are routed to their typical interrupt inputs using the jumper block at J9. This block allows disconnecting or rerouting of the onboard interrupts. The layout of the J9 jumper block is shown here, along with its default settings:

# 2.18 Silicon Disk Configuration

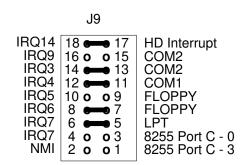

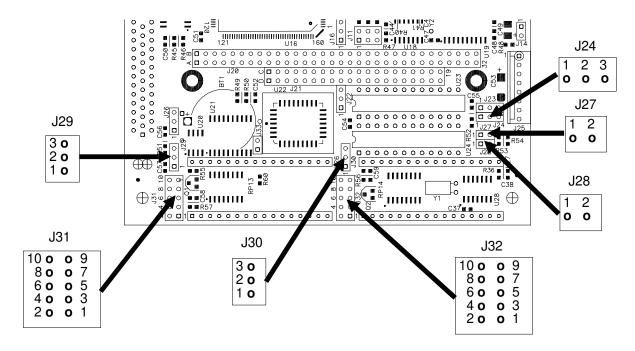

The SAT-DX supports the use of EPROM, PEROM (Flash), SRAM, and the M-Systems' DiskOnChip (DOC) devices to be used as one or more Solid State Disk drives. Section 4 of this manual provides the necessary information for the generation and usage of the Silicon drives. This section documents the required hardware configurations for the various types of devices. The two 32-pin JEDEC memory sockets at U26 and U27 are used to contain the RAM, ROM, FLASH, or DOC devices used for the disk. The silicon disk array is memory mapped into a 16K byte hole at segment E400H and has an I/O control register at 1D4H.

#### **2.18.1** Silicon Disk Mode

There are two basic modes of Silicon Disk operation available on the SAT-DX. The first uses the onboard BIOS extension and supports the use of 512K or 1M EPROMS, 512K SRAMs, or 512K ATMEL Flash devices. The second mode uses the M-Systems' DiskOn-Chip device. The mode is controlled via the jumper block at J28 as shown here:

<u>Note:</u> Jumpering for DOC mode with EPROMs, RAMs, or FLASH devices installed effectively acts to disable the Solid State Disk and similarly when a DOC device is installed and the jumper is selected for standard devices the DOC is disabled.

#### **2.18.2** Device Size Selection

The onboard Solid State Disk array supports either 512K EPROMs, SRAMs, or FLASH devices or 1M EPROM devices. The device size selection is made at J24 as shown here:

NOTE: The device size jumper setting is irrelevant in the DOC mode.

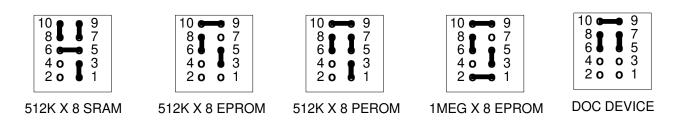

# **2.18.3** Device Type Selection

Each of the sockets in the array also has an individual device type jumper block at the device socket. J31 sets the device type for U26 and J32 sets the device type for U27. The supported device type jumperings are shown here:

# **2.18.4** Battery Backup Selection

When using SRAM devices and nonvolatile operation is desired, battery backup can be selected on a socket by socket basis. J30 for U27 and J29 for U26. The illustration below shows the jumpering for battery backup or standard operation.

**NOTE:** Having the jumper(s) selected for battery backup when using other than low-power-standby SRAMs (such as with EPROMs, or PEROMs) will result in the quick draining of the onboard battery.

#### **2.18.5** Write Protect Control

When using SRAM or PEROM devices the jumper block at J27 can be used as a hard-ware write-protect. With J27 installed the BIOS will not allow writes to the disk array. Note that this jumper has no effect on DOC operations.

#### **2.18.6** Silicon Disk Notes

- 1. When installing devices, U27 is the first device in the array and must always contain the first device of a bootable disk including the DiskOnChip option.

- 2. The DiskOnChip option must use the socket at U27. When a DOC is installed U26 is not usable for any purpose.

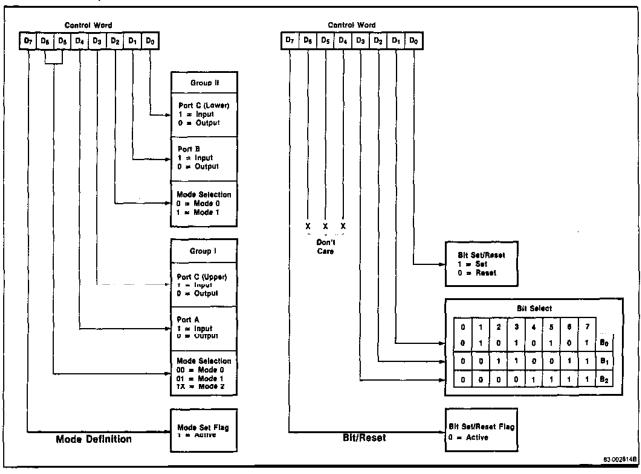

# 2.19 Parallel I/O

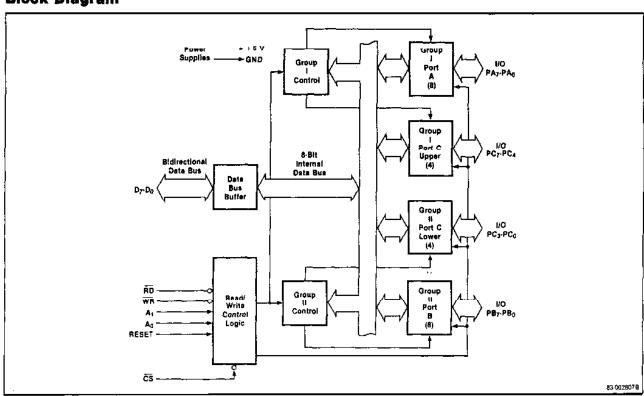

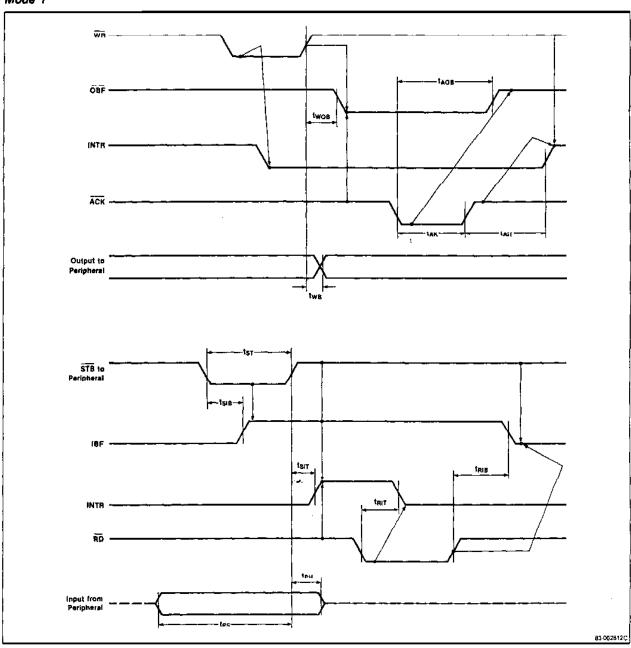

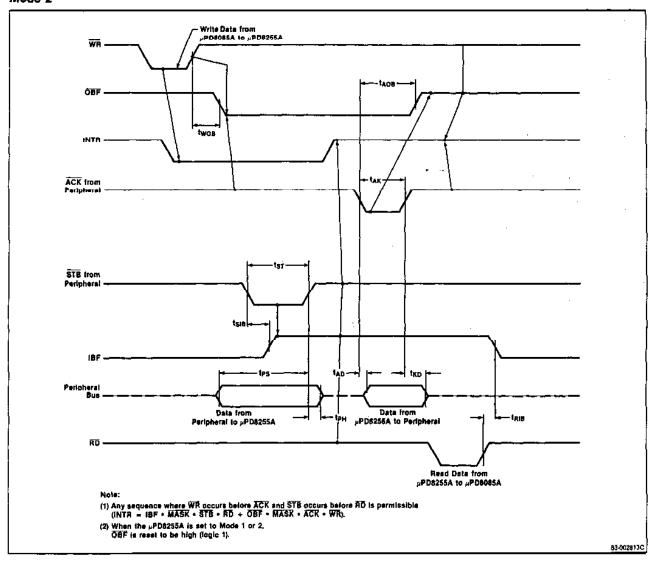

The SAT-DX contains an 8255 type device supporting 24 line of digital I/O. These 24 lines are terminated at J7. The base I/O address of the 8255 is 50H. refer to Appendix F for programming information on the 8255. The pin definitions for the J7 connector are shown here:

|                                                                                                                                                                                                                                                                                                                                                                                                       | J                                                                                                                         | 7                                                                                                                                                                  |                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Port C Bit 7 Port C Bit 6 Port C Bit 5 Port C Bit 3 Port C Bit 3 Port C Bit 1 Port C Bit 1 Port C Bit 1 Port C Bit 0 Port B Bit 7 Port B Bit 5 Port B Bit 5 Port B Bit 3 Port B Bit 3 Port B Bit 1 Port B Bit 7 Port B Bit 7 Port B Bit 7 Port B Bit 7 Port A Bit 7 Port A Bit 7 Port A Bit 5 Port A Bit 5 Port A Bit 5 Port A Bit 5 Port A Bit 1 | 1 0 0 5 7 0 0 1 1 3 0 0 1 1 5 0 0 1 1 5 0 0 1 1 5 0 0 1 1 7 0 0 2 2 5 0 0 0 2 5 0 0 0 3 3 5 0 0 0 4 1 0 0 0 4 7 0 0 4 9 0 | 0 2<br>0 4<br>0 6<br>0 8<br>0 10<br>0 12<br>0 14<br>0 0 18<br>0 20<br>0 22<br>0 24<br>0 26<br>0 30<br>0 32<br>0 34<br>0 36<br>0 40<br>0 42<br>0 44<br>0 46<br>0 50 | GNDD<br>GNDD<br>GNDD<br>GNDD<br>GNDD<br>GNDD<br>GNDD<br>GNDD |

\*NOTE: Pin 49 of J7 may be configured to supply + 5 Volts to pin 49 by placing a jumper on J14. The current draw from pin 49 should not exceed 300mA.

# 2.20 I/O Connector

The I/O to the serial channels, the printer port, and keyboard are all terminated via the connector at J2. An adapter cable part number CBL-162-1 is available from WinSystems to adapt to the conventional I/O connectors. The pin-out for J2 is shown here:

|                                                                                                                                                                                                                                                 | J2                                                                                                                                                                                                            | 2                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COM1 - DCD COM1 - RXD COM1 - TXD COM1 - DTR COM1 - GND COM2 - DSR COM2 - RTS COM2 - CTS COM2 - RI LPT - STROBE LPT - PD0 LPT - PD1 LPT - PD3 LPT - PD4 LPT - PD5 LPT - PD5 LPT - PD7 LPT - BUSY LPT - BUSY LPT - SLCT KEYBD - KDATA KEYBD - +5V | 1 0 3 0 0 7 9 0 0 11 0 0 15 0 0 17 0 0 17 0 0 17 0 0 17 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 17 0 0 0 0 | 0 2 4 6 8 10 12 14 0 18 0 20 22 24 0 28 0 33 34 0 38 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | COM1 - DSR COM1 - RTS COM1 - RTS COM1 - RI COM2 - DCD COM2 - RSX COM2 - TXD COM2 - DTR COM2 - GND LPT - AUTOFD LPT - ERROR LPT - INIT LPT - SLCTIN LPT - GND |

# 2.21 Jumper/Connector Summary

| Connector/<br>Jumper | Description                     | Page Reference     |

|----------------------|---------------------------------|--------------------|

| J 1                  | RS-422/RS-485 I/O Connector     | 2-7, 2-8, 2-9      |

| J 2                  | I/O Connector                   | 2-19               |

| J3                   | Floppy Disk I/O Connector       | 2-12               |

| J4                   | IDE I/O Connector               | 2-12               |

| J5                   | COM2 Configuration Jumper       | 2-5, 2-6, 2-7, 2-9 |

| J6                   | COM1 Configuration Jumper       | 2-5, 2-6, 2-7, 2-8 |

| J7                   | 8255 Parallel I/O Connector     | 2-18               |

| J8                   | CPU Speed Shift Enable Jumper   | N/A                |

| J9                   | Interrupt Routing Header        | 2-15               |

| J 10                 | Not Used                        |                    |

| J11                  | CPU Speed Select Jumper         | 2-2                |

| J12                  | Processor Type Select           | 2-1                |

| J13                  | NMI Routing Jumper              | 2-1                |

| J 14                 | Parallel I/O Vcc Routing Jumper | 2-18               |

| J 15                 | Processor Type Select           | 2-1                |

| J16                  | ECP DRQ Select Jumper           | 2-10               |

| J 17                 | Cache Control Jumper            | 2-1                |

| J18                  | Processor Type Select           | 2-1                |

| J19                  | Processor Type Select           | 2-1                |

| J20                  | PC/104-8 Bus Connector          | 2-11               |

| J21                  | PC/104-16 Bus Connector         | 2-11               |

| J 22                 | ECP DACK Select Jumper          | 2-10               |

| J 23                 | Watchdog Configuration Jumper   | 2-13               |

| J 24                 | SSD Array Size Select Jumper    | 2-17               |

| J 25                 | Power/Reset Connector           | 2-14               |

| J26                  | Master Battery Enable Jumper    | 2-14               |

| J 27                 | SSD Write Protect Jumper        | 2-18               |

| J 28                 | SSD/DOC Mode Select Jumper      | 2-16               |

| J 29                 | U26 Battery Select Jumper       | 2-17               |

| J30                  | U27 Battery Select Jumper       | 2-17               |

| J31                  | U26 Device Configuration Jumper | 2-17               |

| J32                  | U27 Device Configuration Jumper | 2-17               |

| J33                  | Flash Write Enable Jumper       | N/A                |

|                      |                                 |                    |

# 3 AWARD BIOS Configuration

# 3.1 General Information

The SAT-DX comes equipped with a standard Award BIOS with Setup in ROM that allows users to modify the basic system configuration. This type of information is stored in battery-backed CMOS RAM so that it retains Setup information when power is turned off.

# 3.2 Entering Setup

To enter setup, power on the computer and press the DEL key immediately after the message "Press DEL to Enter Setup" appears on the lower left of the screen. If the message disappears before you respond and you still wish to enter setup, restart the system by turning it OFF and then ON or by pressing the RESET button, if so equipped or by pressing the CTRL, ALT and DEL keys simultaneously. Alternately under certain error conditions of incorrect setup the message:

"Press F1 to continue or DEL to Enter Setup"

may appear. To Enter Setup at that time press the DEL key, to attempt to continue, ignoring the error condition, press the F1 key.

# 3.3 Setup Main Menu

The main menu screen is displayed on the following page. Each of the options will be discussed in this section. Use the arrow keys to highlight the desired selection and press ENTER to enter the sub-menu or to execute the function selected.

#### ROM PCI/ISA BIOS (2A4KD000) CMOS SETUP UTILITY AWARD SOFTWARE, INC.

STANDARD CMOS SETUP BIOS FEATURES SETUP CHIPSET FEATURES SETUP LOAD BIOS DEFAULTS LOAD SETUP DEFAULTS PASSWORD SETTING

IDE HDD AUTO DETECTION

SAVE AND EXIT SETUP

EXIT WITHOUT SAVING

Esc : Quit  $\uparrow \downarrow \rightarrow \leftarrow \quad : Select \ Item$  F10 : Save & Exit Setup (Shift) F2 : Change Color

Time, Date. Hard Disk, Type...

# 3.4 Standard CMOS Setup

The items in the Standard CMOS Setup menu are divided into several categories. Each category may include one or more setup items. Use the arrow keys to highlight the item and then use the PgUp, PgDn, +, -, keys to select the desired value for the item.

#### Date

The date format is <day>, <date>, <month>,<year>

day = The day, from Sun to Sat, determined by the BIOS and is display only.

date = The date, from 1 to 31 (or the maximum for the current month)

month = The month, Jan through Dec

year = The year, from 1900 to 2099

#### <u>Time</u>

The time format is < hour > < minute > < second > . The time is calculated on the 24-hour military-time clock, such that 1:00PM is 13:00:00.

#### ROM PCI/ISA BIOS (2A4KD000) STANDARD CMOS SETUP AWARD SOFTWARE, INC.

Date (mm:dd:yy) : Wed, Sep 25 1996 Time (hh:mm:ss): 13 : 28 : 46

TYPE

Drive C : Auto 0 0 0 0 0 0 AUTO Drive D 0 0 0 0 0 **AUTO** : Auto 0

Drive A: 1.44M, 3.5 in

Drive B: None

HARD DISKS

Video : EGA/VGA

Halt On: No Errors

Base Memory: 640K

Extended Memory: 19456K Other Memory: 384K

Total Memory:

CYLS HEAD PRECOMP LANDZ SECTOR MODE

ESC : Quit  $\uparrow \downarrow \rightarrow \leftarrow$  : Select Item F1 : Help (Shift) F2 : Change Color

SIZE

PU/PD/+/- : Modify

#### Drive C: type/Drive D: type

This category identifies the type of hard disk C: or hard disk D: that have been installed in the system. There are 46 predefined types and a user definable type. Types 1-46 are predefined as shown in the following table.

| Type | Size | Cylinders | Heads | Sectors | Precomp | Landzone |

|------|------|-----------|-------|---------|---------|----------|

| 1    | 10   | 306       | 4     | 17      | 128     | 305      |

| 2    | 20   | 615       | 4     | 17      | 300     | 615      |

| 3    | 30   | 615       | 6     | 17      | 300     | 614      |

| 4    | 62   | 940       | 8     | 17      | 512     | 940      |

| 5    | 46   | 940       | 6     | 17      | 512     | 940      |

| 6    | 20   | 615       | 4     | 17      | None    | 615      |

| 7    | 30   | 462       | 8     | 17      | 256     | 511      |

| 8    | 30   | 733       | 5     | 17      | None    | 733      |

| 9    | 112  | 900       | 15    | 17      | None    | 901      |

| 10   | 20   | 820       | 3     | 17      | None    | 820      |

| 11   | 35   | 855       | 5     | 17      | None    | 855      |

| 12   | 49   | 855       | 7     | 17      | None    | 855      |

| 13   | 20   | 306       | 8     | 17      | 128     | 319      |

| 14   | 42   | 733       | 7     | 17      | None    | 733      |

| 15   |      | Reserved  |       |         |         |          |

| 16   | 20   | 612       | 4     | 17      | 0       | 663      |

WinSystems - "The Embedded Systems Authority"

| 17 | 40  | 977  | 5  | 17 | 300    | 977  |

|----|-----|------|----|----|--------|------|

| 18 | 56  | 977  | 7  | 17 | None   | 977  |

| 19 | 59  | 1024 | 7  | 17 | 512    | 1023 |

| 20 | 30  | 733  | 5  | 17 | 300    | 732  |

| 21 | 42  | 733  | 7  | 17 | 300    | 732  |

| 22 | 30  | 306  | 5  | 17 | 300    | 733  |

| 23 | 10  | 977  | 4  | 17 | 0      | 336  |

| 24 | 40  | 1024 | 5  | 17 | None   | 976  |

| 25 | 76  | 1224 | 9  | 17 | None   | 1023 |

| 26 | 71  | 1224 | 7  | 17 | None   | 1223 |

| 27 | 111 | 1224 | 11 | 17 | None   | 1223 |

| 28 | 152 | 1024 | 15 | 17 | None   | 1223 |

| 29 | 68  | 1024 | 8  | 17 | None   | 1023 |

| 30 | 93  | 918  | 11 | 17 | None   | 1023 |

| 31 | 83  | 925  | 11 | 17 | None   | 1023 |

| 32 | 69  | 1024 | 9  | 17 | None   | 926  |

| 33 | 85  | 1024 | 10 | 17 | None   | 1023 |

| 34 | 102 | 1024 | 12 | 17 | None   | 1023 |

| 35 | 110 | 1024 | 13 | 17 | None   | 1023 |

| 36 | 119 | 1024 | 14 | 17 | None   | 1023 |

| 37 | 17  | 1024 | 2  | 17 | None   | 1023 |

| 38 | 136 | 1024 | 16 | 17 | None   | 1023 |

| 39 | 114 | 918  | 15 | 17 | None   | 1023 |

| 40 | 40  | 820  | 6  | 17 | None   | 820  |

| 41 | 42  | 1024 | 5  | 17 | None   | 1023 |

| 42 | 65  | 1024 | 5  | 26 | None   | 1023 |

| 43 | 40  | 809  | 6  | 17 | None   | 852  |

| 44 | 61  | 809  | 6  | 26 | None   | 852  |

| 45 | 100 | 776  | 8  | 33 | None   | 775  |

| 46 | 203 | 684  | 16 | 38 | None   | 685  |

|    |     |      |    |    | 110110 |      |

Press < PgUp> or < PgDn> to select a numbered hard disk type, or type the number and press Enter. Most manufacturers supply hard disk information with their drives than can be used to help identify the proper drive type. Modern IDE drives seldom fall into the predefined types and are usually best handled with the "auto" or "user" defined types. The "auto" mode, reads the hard disk type information at boot time and uses it. The "user" mode allows for either manual or automatic entry, via the setup option "IDE Auto Detect" of the drive parameters.

If you decide to create the user type manually you must supply the required parameters as to Cylinder count, Head count, Precomp Cylinder, Landing Zone Cylinder, and number of sectors per track.

On fixed disks larger than 528MB it will also be necessary to choose the Logical Block Addressing (LBA) mode if you wish the drive to be accessible as a single drive letter.

If there is no hard disk installed be sure to select type "none".

#### Drive A: type/Drive B: type

This category identifies the type of floppy drives attached as Drive A: or Drive B:. The choices are as follows:

NONE 360K, 5.25 in. 1.2M, 5.25 in. 720K, 3.5 in. 1.44M, 3.5 in. 2.88M, 3.5 in.

Note that the standard SAT-DX board does not support the 2.88M floppy drives. If 2.88M floppy support is required, contact your WinSystems' Applications Engineer to inquire about this option.

#### **VIDEO**

This category specifies the type of video adapter used for the primary system monitor that matches your video display board and monitor. The available choices are:

EGA/VGA CGA40 CGA80 MONO

It is recommended that if no display card is present that EGA/VGA be chosen.

#### **Error Halt**

This category determines whether the system will halt if a nonfatal error is detected during the power up self test. The choices are:

No Errors: The system will not be stopped for any error that may be detected.

All Errors: Whenever the BIOS detects a nonfatal error the system will be stopped and a prompt will appear.

All, but Keyboard: The system will not stop for a keyboard error, it will stop for all other errors.

All but Diskette: The system will only stop on Disk errors. All other will be ignored.

All but Disk/Key: All errors except disk and keyboard will result in a halt and a prompt.

#### Memory

This category is display only and is determined by the BIOS POST (Power On Self Test).

#### **Base Memory**

The post routines in the BIOS will determine the amount of base (or conventional) memory installed in the system. The value of the base memory is typically 640K for systems with a Megabyte or greater of RAM installed.

#### **Extended Memory**

The BIOS determines how much extended memory is present during the POST. This is the amount of memory located above 1MB in the CPU's memory address space.

#### Other Memory

This refers to memory located in the 640K to 1024K address space. This is memory that can be used for different applications. DOS may use this area to load device drivers and TSRs to keep as much base memory free as possible for application programs. The most common use of this area is for Shadow RAM.

# 3.5 BIOS Features Setup

#### Virus Warning

This option when enabled, protects the boot sector and partition table of the hard disk against unauthorized write through the BIOS. Any attempt to alter these areas will result in an error message and a prompt to authorize the activity or not.

#### **CPU Internal Cache**

This option when enabled provides maximum performance by caching instructions and data using the on-chip cache of 486 processors.

#### **Quick Power On Self Test**

This option when enabled, speeds up the POST during power up. If it is enabled the BIOS will shorten and/or skip some test items during POST.

# ROM PCI/ISA BIOS (2A4KD000) BIOS FEATURES SETUP AWARD SOFTWARE, INC.

Virus Warning : Disabled Video BIOS Shadow : Enabled

CPU Internal Cache : Enabled C8000-CFFFF Shadow : Disabled D0000-D7FFF Shadow : Disabled

Quick Power On Self Test : Enabled D8000-DFFFF Shadow : Disabled D8000-DFFFF Shadow : Disabled

Boot Sequence : A,C

Swap Floppy Drive : Disabled

Boot Up Floppy Seek : Disabled

Boot Up NumLock Status : Off

Boot Up System Speed : High

Gate AZO Option : Fast

Typematic Rate Setting : Disabled

Typematic Rate (Chars/Sec) : 6

ESC : Quit  $\uparrow \downarrow \rightarrow \leftarrow$  : Select Item

Typematic Delay (Msec) : 250 F1 : Help PU/PD/+/- : Modify Security Option : Setup F5 : Old Value Shift) F2 : Color

F6 : Load BIOS Defaults

#### **Boot Sequence**

This option determines the boot attempt sequence for the fixed disk and floppy disk. The choices are:

C,A System will attempt Hard disk boot first

A,C System will attempt Floppy disk boot first

#### Swap Floppy Drive

This option allows for swapping of the A: and B: floppy drives without actually relocating the drives on the cable.

#### **Boot Up Floppy Seek**

During POST, when this option is enabled, the BIOS will determine if the floppy drive is 40 tracks or 80 tracks. If disabled, no seek test will be performed and no error can be reported.

#### **Boot Up Numlock Status**

This allows user selection of the Numlock state at Boot time.

#### **Boot Up System Speed**

This option allows specification of the processor speed at boot time. The options are:

FAST SLOW

#### Gate A20 Option

This option allows selection of the source for the gate A20 signal. The choices are:

Normal - Sourced from keyboard controller Fast - Sourced from the Chipset

#### **Typematic Rate Setting**

This enables or disables typematic rate programming at boot time. Typematic is the auto-repeat function for the keyboard.

#### Typematic Rate

When the typematic rate setting is enabled the typematic repeat speed is set via this option. The supported rates are:

6 characters per second

8 characters per second

10 characters per second

12 characters per second

15 characters per second

20 characters per second

24 characters per second

30 characters per second

#### Typematic Delay

When typematic rate setting is enabled, this option specifies the time in milliseconds before auto-repeat begins. The supported values are:

250mS

500mS

750mS

1000mS

# Security Option

This option allows you to limit access to the system and setup or just to setup. The choices are:

- System The system will not boot and access will be denied if the correct password is not entered at the prompt.

- Setup The system will boot, but access to Setup will be denied if the correct password is not entered at the prompt.

**NOTE:** To disable security, select "Password Setting" at the Setup Main Menu and then you will be asked to enter a password. Do not type anything but just hit ENTER. Once the security is disabled, the system will boot and you can enter Setup freely.

# **Shadowing Options**

When shadowing for a particular address range is enabled, it instructs the BIOS to copy the BIOS located in ROM into DRAM. This shadowing from an 8-bit EPROM into fast 32-bit DRAM results in a multi-magnitude performance increase. The main BIOS is shadowed automatically but there are other areas that may be selected for shadowing. There areas available for shadowing are shown here:

Video BIOS Shadow - C000-C7FFF EGA/VGA BIOS ROM C8000-CFFFF D0000-D7FFF D8000-DFFFF

# 3.6 Chipset Features Setup

The options in this section control the chipset programming at boot time. In most cases, the default settings should be used unless you have a clear understanding of the significance of the change. It is possible using these options to create a system that will either not boot at all or is very unstable or unreliable. If this should occur, there are two alternatives to return the system to a stable configuration. If the system works well enough to get into Setup, simple choose the "Load BIOS Defaults" option and then "Save and Exit Setup" to restore to factory defaults. If the system will not run well enough to run setup, it will be necessary to remove the battery source temporarily. Refer to section 2.6 for details on reinitializing the CMOS RAM.

Each of the options for the Chipset Features Menu will be briefly discussed in the pages that follow.

| ROM PCI/ISA BIOS (2A4KD000) CHIPSET FEATURES SETUP AWARD SOFTWARE, INC.            |                         |                                                          |                   |  |  |  |

|------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------|-------------------|--|--|--|

| Auto Configuration                                                                 | : Enabled               |                                                          |                   |  |  |  |

| AT-BUS Clock DRAM Read Timing DRAM Write Timing SRAM Read Timing SRAM Write Timing | : Normal<br>: 3-1-1-1   |                                                          |                   |  |  |  |

| ISA I/O Recovery Fast-Back-to-Back On-Chip Local Bus IDE IDE Buffer for DOS & Win  | : Disabled<br>: Enabled |                                                          |                   |  |  |  |

| IDE HDD Block Mode<br>IDE Primary Master PIO<br>IDE Primary Slave PIO              | : Auto                  | ESC : Quit F1 : Help F5 : Old Value F6 : Load BIOS Defau | Shift) F2 : Color |  |  |  |

# **Auto Configuration**

This option, when enabled, instructs the BIOS to auto-select the proper AT Bus Clock, the DRAM read timing, the DRAM write timing, the SRAM read timing, and the SRAM write timing based upon its determination of CPU speed. The default is "Enabled".

## AT Bus Clk

This option is available when the "Auto Configuration" option is disabled. This allows selection of the speed of the AT-BUS clock. This clock is any one of 5 sub-multiples of the processor oscillator or is a fixed 7.19Mhz. The Choices available are:

7.19Mhz

CLK/3

CLK/4

CLK/5

CLK/6

CLK/8

# **DRAM Read Timing**

This option controls the read timing to the DRAM array. The available options are shown here:

```

slow

normal - default

fast

fastest

```

# **DRAM Write timing**

This option control the write timing to the DRAM array. The available options are shown here:

```

slow

normal - default

fast

fastest

```

# **SRAM Read Timing**

This option allows for the selection of timing patterns used to access the cache RAM. The available choice are:

```

2-1-1-1

3-1-1-1 Default

3-2-2-2

4-2-2-2

```

# **SRAM Write timing**

This option controls the number of wait states to be inserted during cache write operations. The choices are:

```

0 Wait

1 Wait Default

```

## ISA I/O Recovery

The CPU and local bus are much faster than the standard for the ISA bus. Selecting Enabled, allows additional time for I/O devices to respond to the system, otherwise data could be lost. The default setting is Enabled.

## Fast Back-to-Back

When Enabled, consecutive write cycles targeted to the same slave become fast back-to-back on the PCI bus. The default setting is Disabled.

# On-Chip Local BUS IDE

This option when enabled allows usage of the onboard local bus IDE controller. The default is Enabled.

## IDE Buffer for Dos & Win

Select Enabled to increase throughput to and from IDE devices by using the on-chip read-ahead and post-write IDE buffers. Note that the use of the buffers may cause some slow IDE devices to appear even slower. The default is Enabled.

## IDE HDD Block Mode

Block mode is also called block transfer, multiple command, or multiple sector read/write. If the IDE hard drive supports block mode, select Enabled for automatic detection of the optimal number of block reads/writes per sector that the drive can support. The default is disabled.

## **IDE Primary Master PIO**

There are 5 transfer modes available for hard disk IDE transfers ranging from mode 0 to mode 4 with each successive mode providing an increased level of performance. Selecting Auto will allow the BIOS to automatically select the optimum transfer mode for the master hard disk. The default is Auto.

# **IDE Primary Slave PIO**

Like the previous item, this option allows for the selection of any one of 5 IDE transfer modes or an Auto selection which allows the BIOS to auto-optimize the IDE transfers to/from the slave drive. The default is Auto.

# 3.7 Load BIOS Defaults

This main-menu option will cause the CMOS to be loaded with the default values assigned by the factory. These are usually considered safe values and do not necessarily represent the highest performance values.

# 3.8 Load Setup Defaults

The options will cause the CMOS to be loaded with the default Setup values assigned by the factory. These are usually values that were determined to give a higher level of performance along with reliable operation.

# 3.9 Password Setting

This option allows the setting of the security password. Pressing Enter at the password prompt disables the security function completely.

# 3.10 IDE HDD Auto Detection

This function allows modern IDE fixed disks to be used to their maximum potential by interrogating the drive as to its preferred configuration of tracks, heads, and sectors and automatically loading these parameters into a "user defined" hard disk type.

# 3.11 Save & Exit Setup

This function writes all changes to CMOS RAM and restarts the system.

# 3.12 Exit without Saving

This option exits Setup without saving any changes made and then restarts the system.

WinSystems - "The Embedded Systems Authority"

THIS PAGE INTENTIONALLY LEFT BLANK

# 4 SAT-DX Silicon Disk Reference

# 4.1 Introduction

Win Systems provides silicon disk support for the SAT-DX using four different media types depending upon the needs of the application.

- 1. The SAT-DX provides support for a bootable ROMDISK with a size of up to 1.44 Megabytes. A simple disk imaging technique allows for the easy creation and maintenance of ROMDISKS. Since the bootable ROMDISK is an exact image of a bootable floppy diskette, all testing and debugging can be accomplished using a floppy drive. Once the application is ready for ROM, it's a simple matter to use the MKDISK utility to create the EPROM files necessary for the bootable ROMDISK equivalent of the functioning floppy diskette.

- 2. In applications requiring occasional program or data updates PEROM (Flash) disks of up to 1 Megabyte may be used as the boot media. Onboard support is provided for the formatting, reading, and writing of the Floppy drive emulating PEROMS.

- 3. For Applications needing to log data, update the application, or for convenience during development, battery backed SRAM may be used as the boot media with a size of up to 1 Megabyte.

- 4. The SAT-DX supports the M-Systems' Disk-On-Chip Devices (DOC). These are single chip devices containing the BIOS Extension, TFFS Flash File System, and a Flash array ranging in size from 2 Megabyte to 72Megabytes. These devices emulate a Hard disk at the BIOS level.

# 4.2 ROMDISK Usage

MKDISK is a menu driven utility for creating the ROM image(s) duplicating the desired floppy diskette. MKDISK is invoked at the DOS command line with:

## **MKDISK**

Select the USSD mode from menu number 1. The other menu options are used with other Win Systems' Silicon Disk systems and are NOT compatible with the SAT-DX board.

MKDISK - Solid State RomDisk Creation Utility V6.00 (C) 1988-1994, WinSystems Inc.

#### SELECT SSD TYPE

Paged Memory Mode (SSD-XT)

Extended Memory Mode (SSD-AT)

V53 Expanded Memory Mode

I/O Mapped Silicon Disk (USSD)

sx386 On Board ROMDISK

SBC53sx Expanded Memory Mode

SAT-V40 Expanded Memory Mode

Use arrow keys and ENTER to make your selection.

#### MKDISK - Main Menu

From menu number 2 select the appropriate source disk size and type.

MKDISK - Solid State RomDisk Creation Utility V6.00 (C) 1988-1994, WinSystems Inc.

## SELECT SOURCE DISK TYPE

160 KB 5 1/4 Single Sided 8 Sectors 40 tracks 180 KB 5 1/4 Single Sided 9 Sectors 40 tracks 320 KB 5 1/4 Double Sided 8 Sectors 40 tracks 360 KB 5 1/4 Double Sided 9 Sectors 40 tracks 720 KB 3 1/2 Double Sided 9 Sectors 80 tracks 720 KB 5 1/4 Double Sided 9 Sectors 80 tracks 954 KB 3 1/2 Double Sided 9 Sectors 53 tracks 960 KB 5 1/4 Double Sided 15 Sectors 64 tracks 1.2 Meg 5 1/4 Double Sided 15 Sectors 80 tracks 1.4 Meg 3 1/2 Double Sided 18 Sectors 80 tracks

Use arrow keys and ENTER to make your selection.

MKDISK - Drive type Menu

MKDISK - Solid State RomDisk Creation Utility V6.00 (C) 1988-1994, WinSystems Inc.

SELECT SOURCE DRIVE

Drive A:

Drive B:

Use arrow keys and ENTER to make your selection.

MKDISK - Drive Menu

Select the source drive as appropriate.

MKDISK - Solid State RomDisk Creation Utility V6.00 (C) 1988-1994, WinSystems Inc.

**SELECT ROM SIZE**

32K X 8 ROM (27C256 type)

64K X 8 ROM (27C512 type)

128K X 8 ROM (27C010 type)

256K X 8 ROM (27C020 type)

512K X 8 ROM (27C040 type)

1M X 8 ROM (27C080 type)

Use arrow keys and ENTER to make your selection.

MKDISK - ROM type Menu

From menu number 4 select the appropriate EPROM size for the ROMDISK. EPROM sizes smaller than 512K or not usable with the SAT-DX, but are provided as choices with other silicon disk devices.

MKDISK - Solid State RomDisk Creation Utility V6.00 (C) 1988-1994, WinSystems Inc.

SELECT OUTPUT FILE TYPE

Binary Image Files

Hex ROM Image Files

S-Record ROM image files

Use arrow keys and ENTER to make your selection.

#### MKDISK - Output Menu

From menu number 5 select the appropriate ROM image file format that your EPROM programmer accepts. Selecting the Binary ROM image file format will result in the smallest files. MKDISK will then read the specified floppy diskette and create a ROMx.HEX or ROMx.S19 where x is the ROM number in the sequence (starting with 1) and the extension (.BIN, .HEX, .S19) indicates the output format for Binary, Hex, and Motorola respectively. If more than one file is created it means that the disk will span more than a single EPROM. Once the ROM(s) have been created using the image files, install the ROM(s), jumper for correct ROM size, and enable the Silicon Disk boot option. The next power up should result in a boot from the A: Silicon Disk. The actual floppy drive, if present, will then be available as drive B:.

# 4.3 Bootable RAMDISK usage

The SAT-DX supports bootable RAMDISKs of up to 1 Megabyte in size. 512K X 8 Static RAMs/PEROMs can be installed in the board beginning at U27. One or two RAMs/PEROMs can be installed and the device jumpers should be appropriately set as described in section 2.20. After powerup it is necessary to configure the silicon disk for the actual size of the drive using the SSDINIT utility. SSDINIT is invoked at the DOS command line with:

SSDINIT [A: | B: ] disk\_size[K | M]

the K or M arguments are optional and are actually ignored. Values below 32 are assumed to be in Megabytes while values above 32 are assumed to be in Kilobytes. An example might help to clarify. To prepare a 1meg FLASH or SRAM disk for formatting type:

SSDINIT B: 1M

The disk is new and prepared for formatting. The system must be rebooted prior to formatting with the simple DOS command:

format b: /s/u

After the next reset the formatted silicon disk will boot as the A: drive. If it is ever necessary to bypass the silicon disk boot in order to reformat or to boot the actual floppy drive, or the hard disk, simply press the < CTRL> < ALT> < LSHIFT> keys simultaneously immediately following display of the BIOS configuration BOX. The message:

Silicon Disk Boot Aborted by User

will be displayed and the system will boot from one of the available boot drives.

**IMPORTANT NOTE:** The FLASHDISK is fully writeable at all times but is not recommended for continuous updating or data logging. The onboard BIOS implements a simple FAT based file system (identical to a floppy disk) with no wear leveling implemented. The PEROMS can and will wear out with excessive write cycles. ATMEL specifies at least 10,000 write cycles.

# 4.4 Non-Bootable RAMDISK Usage

A non-bootable RAMDISK is often desired in conjunction with a bootable ROMDISK, FLASHDISK, or rotational media. It can then be used for program updates, parameter storage, or data logging applications. a non-bootable RAMDISK uses the WinSystems' Universal Solid State Disk Driver (USSD) which is loaded via the boot media's CONFIG.SYS file with the entry:

device = ussd.sys /mod:p /pad:1d4 /seg:e400 /psz:16 /inc:1 /spg:xx /dsz:yy

where the YYY in /DSZ:YYY is the size of the disk in Kilobytes and the XXX in the /SPG:XXX is the starting page address in the array for this silicon disk. This hexadecimal value is actually the count of 16K byte blocks preceding the start of the RAMDISK. The simplest approach is to use the table below to determine the correct /SPG value.

| Total RAM/ROM/FLASH Prior to this socket | /SPG Value |

|------------------------------------------|------------|

| None                                     | /SPG:80    |

| 512K                                     | /SPG:A0    |

| 1M                                       | /SPG:C0    |

## WinSystems - "The Embedded Systems Authority"

A couple of examples might help to illustrate. Suppose we're booting from a floppy or hard disk and we have installed two 512K X 8 SRAMs. In order to create the desired 1 Meg RAMDISK we would need the line:

device = ussd.sys /mod:p /seg:e400 /psz:16 /inc:1 /pad:1d4 /spg:80 /dsz:1024

which would indicate that we wish to create a disk of 1M(1024K) starting at the beginning of the array.

For another example assume that we want a 512K ROMDISK and a 512K RAMDISK. We would create our bootable floppy with the CONFIG.SYS line:

device = ussd.sys /mod:p /pad:1d4 /seg:e400 /psz:16 /inc:1 /spg:a0 /dsz:512

which would create the 512K RAMDISK which will be preceded by the 512K of ROM-DISK. We would create our ROMDISK as previously described and place the EPROM into U27. We would install our 512K SRAM into U26.

A final example would be to use the non-bootable RAMDISK in U26 as a secondary silicon disk to a DISK-ON-CHIP. In this case we are booting from the DISK-ON-CHIP and will include the following CONFIG.SYS command line: